台積電大舉擴展超低耗電製程陣容。為搶占物聯網(IoT)與穿戴電子商機,台積電29日搶先發布超低耗電(ULP)技術平台,提供從0.18微米到16奈米鰭式電晶體(FinFET)等一系列超低耗電製程,協助客戶打造更低功耗且整合度更高的系統元件。

台積電董事長張忠謀曾表示,物聯網將是電子產業下一個大事(Next Big Thing),並點名低功耗、系統級封裝(SiP)及感測技術將是支撐物聯網發展的三大支柱。其中,低功耗設計更已成為半導體供應鏈業者一致追求的目標,將牽動一連串製程、IC設計技術轉變。

事實上,物聯網和穿戴式電子裝置對晶片耗電量的規格要求遠勝於行動裝置,因此,台積電日前已將適用於行動元件製造的低耗電製程,進一步升級為可滿足下世代物聯網和穿戴電子晶片設計的超低耗電製程,並組成覆蓋多元節點和應用的技術平台,以因應各類型元件研發需求。

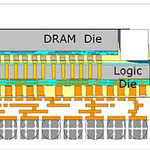

據悉,超低耗電技術平台涵蓋0.18微米極低漏電製程(0.18eLL)、90奈米超低漏電製程(90uLL)及16奈米FinFET製程,且能支援高達1.2GHz運算速度;針對特殊製程應用,台積電更在該平台納入嵌入式記憶體專用的55奈米超低耗電製程(55ULP)、專攻射頻元件的40奈米超低耗電製程(40ULP),以及鎖定SoC設計的28奈米超低耗電製程(28ULP)。

相較前一代製程方案,超低耗電技術平台將可實現更高層級的晶片系統整合,並降低晶片操作電壓達20~30%,大幅減少動態與靜態功耗,以延長系統電池使用時間達二至十倍。台積公司總經理暨共同執行長劉德音強調,低功耗及無所不在的連結功能已是物聯網成功的關鍵,而台積電搶先業界推出完備的超低耗電技術平台,將有助催化物聯網技術發展與創新。

此外,晶片商亦可充分利用台積電開放創新平台(OIP)所提供的矽智財(IP)設計生態環境,為使用超低耗電技術平台的產品增添許多功能應用價值。益華電腦(Cadence)資深副總裁暨策略長徐季平指出,看好台積電超低耗電技術平台在物聯網晶片市場的發展潛力,益華也積極爭取合作機會,並已成功將旗下記憶體、類比、介面、基頻、影音處理和臉部辨識等IP及相應開發工具,置入超低耗電技術平台,可望協助晶片商提升產品功能和上市速度,迎合物聯網和穿戴電子快速改朝換代的生命週期。

舉例來說,當晶片開發人員欲進行全新的超低耗電製程設計時,可重覆利用製程矽智財與元件資料庫,以提高首次設計即生產成功的機率,達到產品迅速上市的目標。

台積電已預計在2014年底前與客戶達成數項設計合作案,包括55奈米、40奈米及28奈米超低耗電製程,並將於2015年展開試產。